# REALM: PERFORMANCE PORTABILITY THROUGH COMPOSABLE ASYNCHRONY

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Sean Jeffrey Treichler December 2016

© 2016 by Sean Jeffrey Treichler. All Rights Reserved. Re-distributed by Stanford University under license with the author.

This work is licensed under a Creative Commons Attribution-Noncommercial 3.0 United States License. http://creativecommons.org/licenses/by-nc/3.0/us/

This dissertation is online at: http://purl.stanford.edu/hn774ry7741

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

#### Alex Aiken, Primary Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

#### Pat Hanrahan

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

#### **Philip Levis**

Approved for the Stanford University Committee on Graduate Studies.

#### Patricia J. Gumport, Vice Provost for Graduate Education

This signature page was generated electronically upon submission of this dissertation in electronic format. An original signed hard copy of the signature page is on file in University Archives.

## Abstract

Modern supercomputers are growing increasingly complicated. The laws of physics have forced processor counts into the thousands or even millions, resulted in the creation of deep distributed memory hierarchies, and encouraged the use of multiple processor and memory types in the same system. Developing an application that is able to fully utilize such a system is very difficult. The development of an application that is able to run well on more than one such system with current programming models is so daunting that it is generally not even attempted.

The Legion project attempts to address these challenges by combining a traditional hierarchical application structure (i.e. tasks/functions calling other tasks/functions) with a hierarchical data model (logical regions, which may be partitioned into subregions), and introducing the concept of mapping, a process in which the tasks and regions of a machine-agnostic description are assigned to the processors and memories of a particular machine.

This dissertation focuses on Realm, the "low-level" runtime that manages the execution of a mapped Legion application. Realm is a fully asynchronous event-based runtime. Realm operations are deferred by the runtime, returning an event that triggers upon completion of the operation. These events may be used as preconditions for other operations, allowing arbitrary composition of asynchronous operations. The resulting operation graph naturally exposes the available parallelism in the application as well as opportunities for hiding the latency of any required communication. While asynchronous task launches and non-blocking data movement are fairly common in existing programming models, Realm makes all runtime operations asynchronous — this includes resource management, performance feedback, and even, apparently paradoxically, synchronization primitives.

Important design and implementation issues of Realm will be discussed, including the novel generational event data structure that allows Realm to efficiently and scalably handle a very large number of events in a distributed environment and the machine model that provides the information required for the mapping of a Legion application onto a system. Realm anticipates dynamic behavior of both future applications and future systems and includes mechanisms for application-directed profiling, fault reporting, and dynamic code generation that further improve performance portability by allowing an application to adapt to and optimize for the exact system configuration used for each run.

Microbenchmarks demonstrate the efficiency and scalability of the Realm and justify some of the non-obvious design decisions (e.g. unfairness in locks). Experiments with several mini-apps are used to measure the benefit of a fully asynchronous runtime compared to existing "non-blocking" approaches. Finally, performance of Legion applications at full-scale show how Realm's composable asynchrony and support for heterogeneity benefit the overall Legion system on a variety of modern supercomputers.

## Acknowledgments

Life is full of team efforts. Nobody crosses the finish line without having a support team to back them up: people that help you train, people that make sure you have the right equipment, people that clear the road ahead of you, and people that give you that emotional support you need when you're too tired to take another step.

As my advisor, Alex Aiken served in all these roles. I arrived at Stanford with a solid idea of what I wanted to build, but little plan for how to do it. Alex helped me turn that long-term vision into the smaller steps needed to make actual progress. He helped me deal with pitfalls along the way, but more importantly, used his experience and intuition to anticipate and avoid many more pitfalls. I'd like to think that I taught Alex a few things along the way, but the balance of knowledge transfer is pretty clearly in the other direction.

Phil Levis and Pat Hanrahan deserve mention too, and not just for slogging through the early drafts of this dissertation. Pat constantly encouraged me to think big and look for ways that my work could be used to solve larger problems. Phil helped me refine my arguments and distill the key ideas on which my work is based.

The faculty and staff in the Computer Science Department at Stanford have constructed an amazing environment for research. I will feel forever guilty about the amount of paperwork that was done (and done cheerfully!) on my behalf, letting me focus on my work. Similarly, the willingness of the folks at NVIDIA to let me run "solo" while staying connected has made it much more likely that my research will be of practical use in future systems.

The Legion project has become a sprawling thing, but it would not exist without fellow founding member Michael Bauer. Working with him to first flesh out a vision for performance portable computing and then prove that it could be done has been a rewarding experience on many levels. Current and former members of Alex's research group have contributed materially to the Legion project (Elliott Slaughter, Wonchan Lee, Zhihao Jia, Todd Warszawski, Rahul Sharma) and/or provided general perspective and the occasional distraction that kept me from losing track of my surroundings (Eric Schkufza, Peter Hawkins, Adam Oliner, Stefan Heule, Manolis Papadakis).

Our work has given us the opportunity to collaborate with many scientists at the Department of Energy's laboratories. All have provided the healthy skepticism that drives research in the first place, but also enthusiasm and support for exploring new approaches to big problems. Outstanding in their enthusiasm and support have been Pat McCormick and Galen Shipman at Los Alamos National Laboratory and Jackie Chen at Sandia National Laboratories.

My family and friends have been with me for every step of this long road. Shoulders to cry on, ears to talk off, smiles of support, and even the occasional nagging all rekindle the fire when the pace begins to drop. In particular, Julie, Naomi, and Lisa remind me every day that the effects of caffeine pale in comparison to those of unconditional love.

At the end of the race, it is my name that will be recorded in the book, but this is not my accomplishment alone. It is a team effort, and I have the best team that I could ask for.

# Contents

| Α        | Abstract              |                                    |    |  |  |  |  |  |

|----------|-----------------------|------------------------------------|----|--|--|--|--|--|

| Α        | Acknowledgments       |                                    |    |  |  |  |  |  |

| 1        | Intr                  | oduction                           | 1  |  |  |  |  |  |

|          | 1.1                   | High Performance Computing         | 3  |  |  |  |  |  |

|          |                       | 1.1.1 Comparisons to Big Data      | 4  |  |  |  |  |  |

|          | 1.2                   | Supercomputers                     | 5  |  |  |  |  |  |

|          | 1.3                   | Bulk-Synchronous Computing         | 6  |  |  |  |  |  |

|          |                       | 1.3.1 Global View of Control       | 7  |  |  |  |  |  |

|          |                       | 1.3.2 Single Program Multiple Data | 8  |  |  |  |  |  |

|          | 1.4                   | Programming Challenges             | 11 |  |  |  |  |  |

| <b>2</b> | The                   | e Latency Gap                      | 12 |  |  |  |  |  |

|          | 2.1                   | Hiding Latency                     | 15 |  |  |  |  |  |

|          | 2.2                   | Implicit Dependencies              | 17 |  |  |  |  |  |

|          | 2.3                   | Explicit Dependencies              | 19 |  |  |  |  |  |

|          | 2.4                   | Microprocessor Design Analogy      | 20 |  |  |  |  |  |

|          | 2.5                   | Related Work                       | 21 |  |  |  |  |  |

| 3        | Heterogeneity         |                                    |    |  |  |  |  |  |

|          | 3.1                   | Hybrid Approaches                  | 25 |  |  |  |  |  |

|          | 3.2                   | Titan                              | 26 |  |  |  |  |  |

|          | 3.3                   | Heterogeneous Heterogeneity        | 28 |  |  |  |  |  |

|          | 3.4                   | Generalized Heterogeneity          | 30 |  |  |  |  |  |

|          | 3.5                   | Related Work                       | 31 |  |  |  |  |  |

| 4        | Composable Asynchrony |                                    |    |  |  |  |  |  |

|          | 4.1                   | From Tasks to Operations           | 34 |  |  |  |  |  |

|   | 4.2          | Heterogeneity and Hybrid Approaches         | 35              |  |  |

|---|--------------|---------------------------------------------|-----------------|--|--|

|   | 4.3          | Deterministic Behavior                      | 35              |  |  |

|   | 4.4          | Application Structure                       | 36              |  |  |

|   | 4.5          | Legion                                      | 36              |  |  |

| 5 | Realm        |                                             |                 |  |  |

| 0 | 5.1          | Realm Objects                               | <b>40</b><br>41 |  |  |

|   | 5.2          | Basic Realm Application                     | 42              |  |  |

|   | 5.2          | Data Model                                  | 42<br>45        |  |  |

|   | 0.0          | 5.3.1 Accessors                             | 46              |  |  |

|   |              | 5.3.2 Relaxed Data Models                   | 40<br>47        |  |  |

|   | 5.4          | Heterogeneous Processors                    | 47              |  |  |

|   | 5.4          | Deferred Resource Management                | 53              |  |  |

|   | 0.0          | 5.5.1 Resource Exhaustion                   | 55              |  |  |

|   | 5.6          | Asynchronous Synchronization                | 55              |  |  |

|   | 0.0          | 5.6.1 Reservations                          | 50              |  |  |

|   |              | 5.6.2 Distributed Reservations and Fairness | 58              |  |  |

|   | 5.7          | Fork-Join Parallelism                       | 58<br>61        |  |  |

|   | 5.7          | External Dependencies                       | 62              |  |  |

|   | 5.0<br>5.9   | Barriers                                    | 64              |  |  |

|   |              | Barners          Futures                    | 66              |  |  |

|   |              | Causality                                   |                 |  |  |

|   | 0.11         | Causanty                                    | 66              |  |  |

| 6 | Gen          | erational Events                            | 69              |  |  |

|   | 6.1          | Basic Events                                | 69              |  |  |

|   | 6.2          | Event Latency and Trigger Rates             | 72              |  |  |

|   | 6.3          | Generational Events                         | 74              |  |  |

|   | 6.4          | Event Lifetimes                             | 76              |  |  |

| 7 | Mac          | chine Model                                 | 79              |  |  |

| • | 7.1          | Machine Model                               | 80              |  |  |

|   | 7.2          | Address Spaces                              | 81              |  |  |

|   | 7.2<br>7.3   | Query Interface                             | 81<br>82        |  |  |

|   | 7.3<br>7.4   | Subscriptions                               | 84              |  |  |

|   | $7.4 \\ 7.5$ |                                             |                 |  |  |

|   |              | Manipulating the Machine                    | 84<br>85        |  |  |

|   | 7.6          | Application Models                          | 85              |  |  |

| 8                | Profiling      |                               | 86  |

|------------------|----------------|-------------------------------|-----|

|                  | 8.1 Measurer   | ments                         | 87  |

|                  | 8.2 Example    | : Task-Level Execution Trace  | 88  |

|                  | 8.3 Example    | : Empirical Work Distribution | 89  |

|                  | 8.4 Profiling  | Realm Itself                  | 95  |

|                  | 8.5 Fault Tol  | lerance                       | 95  |

| 9                | Dynamic Co     | ode Generation                | 97  |

|                  | 9.1 Dynamic    | Loader                        | 99  |

|                  | 9.2 LLVM .     |                               | 99  |

|                  | 9.3 CUDA .     |                               | 100 |

|                  | 9.4 Other Co   | ode Translators               | 101 |

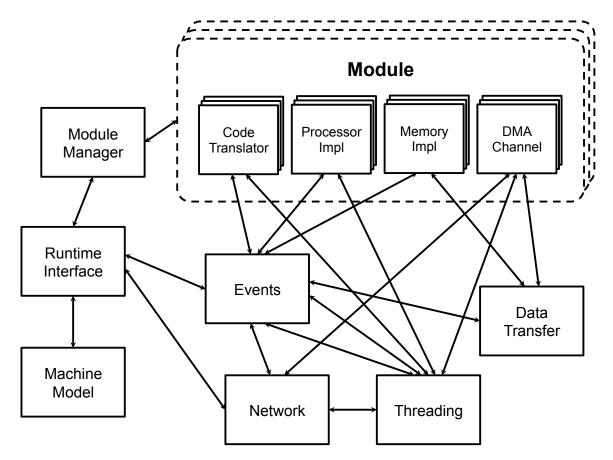

| 10               | Extensibility  | 7                             | 103 |

|                  | 10.1 Events as | nd Scheduling                 | 103 |

|                  | 10.2 Threadin  | ıg                            | 104 |

|                  | 10.3 Data Tra  | unsfer                        | 107 |

|                  | 10.4 Network   |                               | 107 |

|                  | 10.5 Module I  | Interface                     | 109 |

|                  | 10.5.1 M       | Iemory Implementations        | 110 |

|                  | 10.5.2 P       | rocessor Implementations      | 111 |

|                  | 10.5.3 D       | MA Channels                   | 111 |

|                  | 10.5.4 C       | ode Translators               | 111 |

|                  |                | pplication Interaction        |     |

|                  | 10.5.6 Ir      | nter-Module Dependencies      | 112 |

| 11               | Case Study:    | S3D                           | 113 |

|                  | 11.1 S3D       |                               | 113 |

|                  | 11.2 Keenelan  | nd                            | 116 |

|                  |                |                               | 118 |

|                  |                | RCCI                          | 119 |

|                  | 11.5 Piz Dain  | t                             | 124 |

|                  |                |                               | 125 |

|                  | 11.7 Ongoing   | Work                          | 128 |

| 12 Conclusion 12 |                |                               | 129 |

| Bi               | bliography     |                               | 132 |

# List of Figures

| 1.1 | Early Cray Supercomputers                                                                    | 5  |

|-----|----------------------------------------------------------------------------------------------|----|

| 1.2 | Simulation of heat diffusion in UPC                                                          | 7  |

| 1.3 | Simulation of heat diffusion in MPI                                                          | 9  |

| 2.1 | Performance and Latency of World's Fastest Supercomputers                                    | 13 |

| 2.2 | Operations Wasted by Bulk-Synchronous Communication on Fastest Supercomputers                | 14 |

| 2.3 | Simulation of heat diffusion with latency hiding                                             | 15 |

| 2.4 | Undesired scheduling constraints resulting from implicit dependencies $\ldots \ldots \ldots$ | 18 |

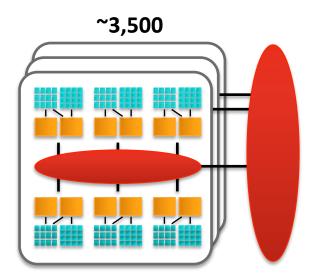

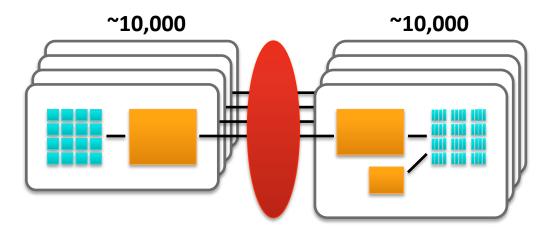

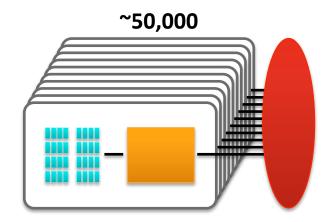

| 3.1 | System Architecture of Titan (Oak Ridge National Laboratory)                                 | 27 |

| 3.2 | System Architecture of Summit (Oak Ridge National Laboratory)                                | 28 |

| 3.3 | System Architecture of Trinity (Los Alamos National Laboratory)                              | 29 |

| 3.4 | System Architecture of Aurora (Argonne National Laboratory)                                  | 30 |

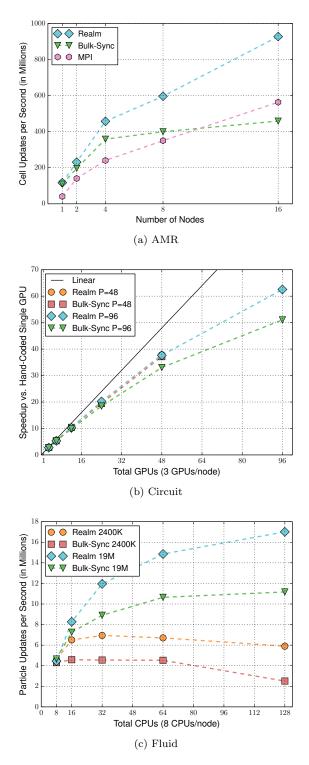

| 4.1 | Performance Comparison of Explicit vs. Implicit Dependencies                                 | 37 |

| 5.1 | Hello world in Realm                                                                         | 44 |

| 5.2 | Portable saxpy in Realm                                                                      | 54 |

| 5.3 | Massively-parallel memory allocation in Realm                                                | 56 |

| 5.4 | Use of Reservation for mutual exclusion                                                      | 59 |

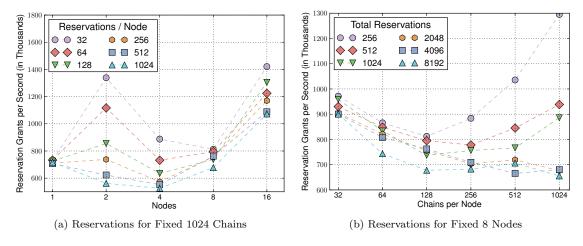

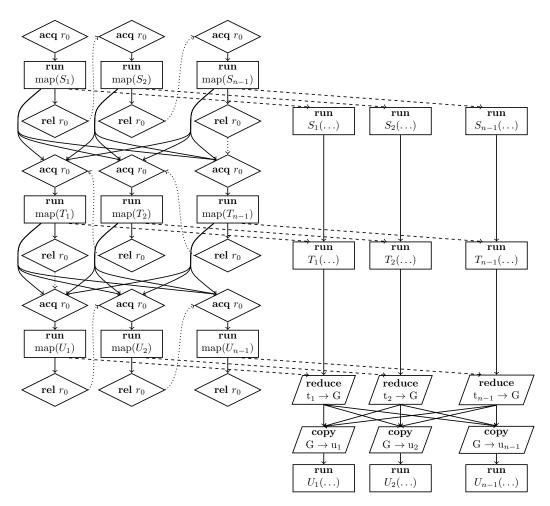

| 5.5 | Microbenchmark Results                                                                       | 61 |

| 5.6 | Implementation of SAXPY kernel using hierarchical decomposition                              | 63 |

| 5.7 | Coordinating ghost cell exchange with a Barrier                                              | 65 |

| 6.1 | A Realm Event Graph                                                                          | 70 |

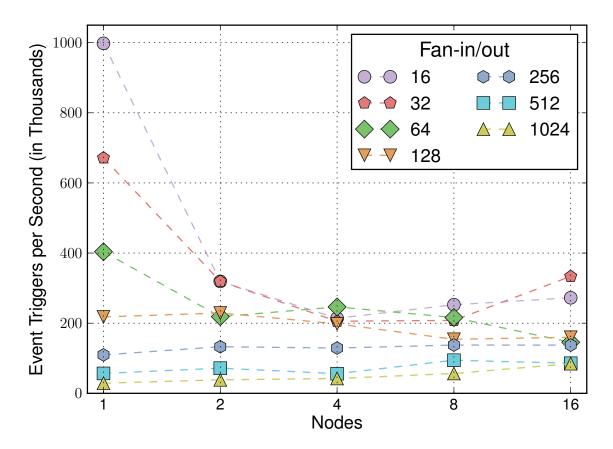

| 6.2 | Event Latency Results                                                                        | 72 |

| 6.3 | Event Trigger Rates                                                                          | 73 |

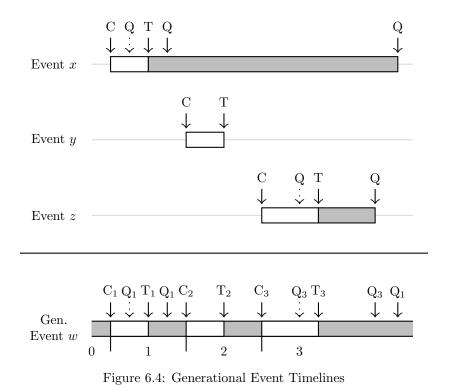

| 6.4 | Generational Event Timelines                                                                 | 74 |

| 6.5 | Event Lifetimes in Fluid Application                                                         | 77 |

| 7.1   | Routine to print Realm machine model affinity graph        | 81  |

|-------|------------------------------------------------------------|-----|

| 7.2   | Visualization of affinity graph for single node of sapling | 82  |

| 8.1   | legion_prof execution timeline                             | 90  |

| 8.2   | Load balancing based on real-time Realm profiling          | 92  |

| 8.3   | Benefits of Empirical Work Distribution                    | 93  |

| 10.1  | Modular Internal Structure of Realm                        | 104 |

| 10.2  | Core Reservation Compatibility Matrix                      | 106 |

| 10.3  | Realm Module Interface                                     | 110 |

| 11.1  | Task Graph for a Single Iteration of S3D's Main Loop       | 115 |

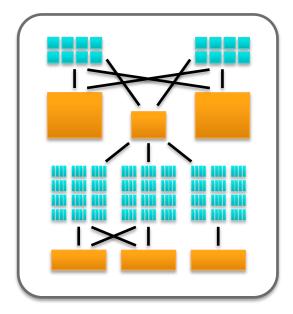

| 11.2  | System Architecture of Keeneland                           | 116 |

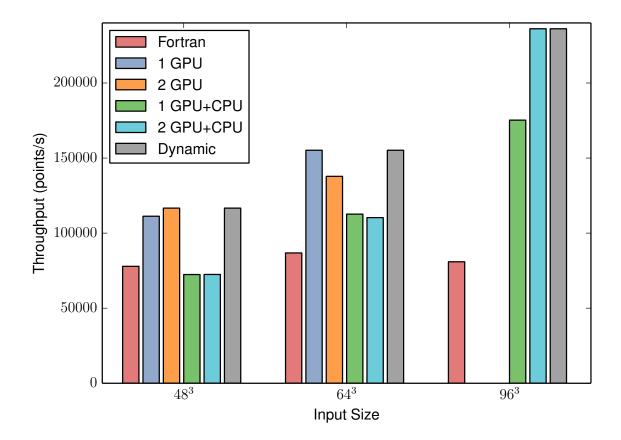

| 11.3  | Mapping Alternatives for S3D on Keeneland                  | 117 |

| 11.4  | S3D Performance Comparison on Titan (heptane mechanism)    | 120 |

| 11.5  | S3D Latency Hiding Comparison on Titan                     | 120 |

| 11.6  | Auto-ignition kernels resulting from compression ignition  | 121 |

| 11.7  | PRF Mechanism Performance in S3D                           | 123 |

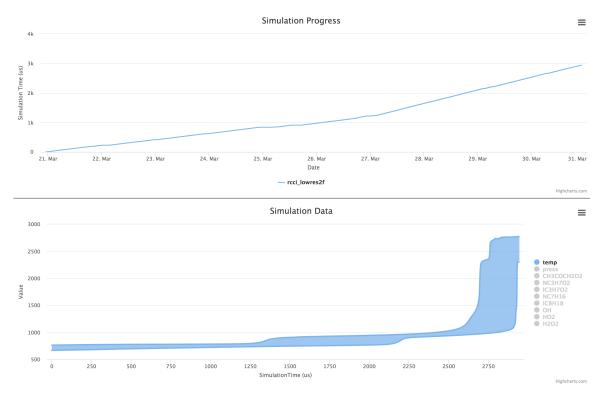

| 11.8  | Progress of RCCI Simulation over Time                      | 125 |

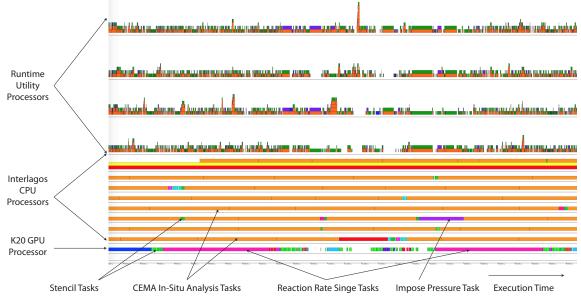

| 11.9  | Scheduling of CEMA Tasks in S3D                            | 126 |

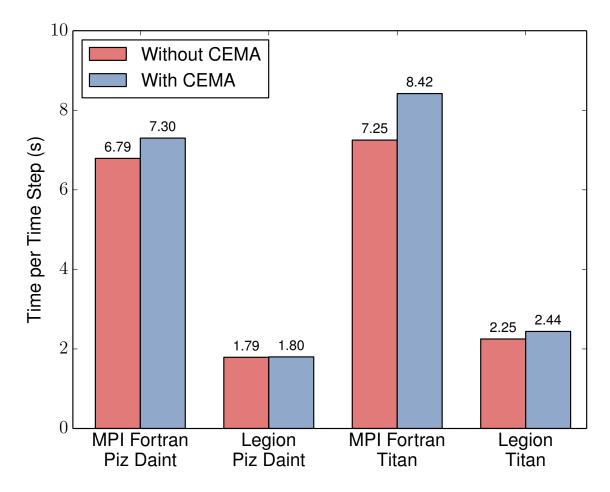

| 11.10 | DExecution Time Impact of CEMA in S3D                      | 127 |

### Chapter 1

### Introduction

The world of high performance computing is in the midst of a programmability crisis. It takes multiple person-years of effort to port such an application to a new supercomputer[18], and that current expectations are that similar efforts will be needed for each new supercomputer architecture that comes online[17]. Today's supercomputers have simply become too hard to program, and while existing tools may allow a programmer, often with significant effort, to achieve good performance on a single target system, *performance portability* (the ability to have the same source code not just run, but run well, on multiple systems) is becoming out of reach. The systems that are planned to come online in the next few years promise an even greater challenge. In this thesis, we present Realm, a runtime system for high performance computing that investigates a basis for a lasting solution to this crisis.

The key idea that drives Realm is that of *composable asynchrony*, the idea that *all* operations performed by the runtime on behalf of the application can be deferred until their inputs are available, and that this deferral is handled by the runtime. Runtime deferral of operations allows the application code to be written in a way that is agnostic to the performance characteristics of the system on which the application is currently running. This agnosticism avoids the primary cause of portability problems: the need to change the original application code to improve performance on a specific machine and the interference between the changes needed for different machines.

We will discuss composable asynchrony and the system of *explicit dependencies* on which it is based at length, but we warn the reader in advance that this will not be sufficient. A comprehensive solution to the problem of performance portability should include the following as well:

- abstractions for the processing and storage resources in the system that allow application code to avoid using architecture- or vendor-specific interfaces for initiating computation or moving data within the system

- the ability to manage, and ideally generate, variants of performance-critical sections of code

for different processor architectures

- a model of the system at runtime, allowing an application to discover what resources are available and how they are connected

- an online profiling framework that provides information about the applications dynamic behavior back to the application itself

- a modular internal design that simplifies the addition of support for new system architecture features

- external interfaces with a clean separation of concerns, anticipating that in many cases, the "application" is actually higher-level runtime(s), library code, and/or even domain-specific language(s)

We believe Realm is currently unique in satisfying all of these requirements, and we offer Realm both as an artifact for use today but also as an argument that the combination of these features in a runtime system is both desirable and feasible.

This thesis is divided into three parts. The first part provides some background. The rest of this chapter describes what we mean when we say "high performance computing" and "supercomputers", and give a quick introduction to *bulk-synchronous programming*, the currently predominant programming style for high performance computing. The following two chapters will discuss the two root causes of the current programmability crisis, the growing latency gap and increases in system heterogeneity. That discussion includes a survey of existing tools and techniques that attempt to address these issues.

The second part forms the bulk of the thesis and describes composable asynchrony, its embodiment in the various components and concepts of Realm, how they work at a high level, and the rationale for the design. Chapter 6 dives a little more deeply into the implementation and benefits of *generational events*, a key reason why Realm can provide its composable asynchrony with low enough overhead to satisfy the needs of high performance computing. The Realm source code consists of over 60,000 lines of code, and the reader will be relieved that almost none of it appears in this thesis. Most of the code snippets are demonstrations of how an application might use Realm's features to attain performance portability.

The final part of the thesis is Chapter 11, an extended case study of the porting, tuning, and adaptation of S3D, a "real" high-performance computing application, to the Legion programming model. Legion uses Realm as its foundation, and this chapter contains the bulk of the experimental results of this thesis, both quantitative and qualitative. However, readers that wish to skip ahead to the results should stop in Chapters 4, 5, and 6, all of which contain results from micro-benchmarks or mini-apps, measuring the benefits and/or overheads of composable asynchrony.

#### **1.1 High Performance Computing**

Although it is a term in everyday use, the exact definition of *high performance computing* (HPC) is difficult to pin down. A common "definition" in use is to say that any application that requires a supercomputer is an HPC application. This suffers from, among other things, the fact that today's personal computers and even smartphones exceed the computational capabilities of the supercomputers of 10-15 years ago. Another approach is to look at various applications that are generally agreed to be "HPC applications" and identify commonalities. For example, the six applications that were used for application readiness testing of the Titan supercomputer at Oak Ridge National Laboratory were:[16]

- S3D, a simulation of the combustion of gases in a turbulent environment (e.g. the interior of an automobile engine)

- WL-LSMS, an application measuring the role of material disorder in nanoscale materials

- NRDF, a simulation of radiation transport, important in the study of astrophysics, laser fusion, medical imaging

- LAMMPS, a molecular model of cell membrane fusion used to study how molecular enter or exit living cells

- CAM-SE, an application that examines climate change adaptation and mitigation scenarios

- Denovo, an alternative approach to modeling radiation transport, especially in the field of nuclear energy

In general, these applications are constructing models of a physical system and then simulating how the system changes under the influence of known physical laws. The absolute scale of the system being modeled can vary from the subatomic to the galactic, and the time over which the system is evolved may vary from nanoseconds to trillions of years.

Other applications might work backwards instead, figuring out what physical laws would explain an observed change in a system. Examples include cosmology simulations that test dark matter hypotheses or reverse time migration, which identifies subterranean features based on seismic wave measurements. Finally, the system being modeled may not always be tangible. It might instead model social interactions for health or commercial reasons, or the complicated connections in today's financial markets.

Whether real or hypothesized, these systems are complicated enough that an exact solution is impossible to obtain. Instead, an approximate solution is computed by discretizing the system into millions or even billions of elements (e.g. atoms, photons, points in the simulation volume) and the timeline into thousands or millions of intervals, or *time steps*. Various properties are tracked for each element (e.g. energy, velocity, temperature) — there may be only a handful or hundreds. The properties are computed for each interval, based on other properties, other elements, and/or other interval. This computation can be very simple (e.g. a single instruction to yield velocity from the difference of positions) or very complicated (e.g. thousands of instructions to determine the net reaction rate of one chemical species based on the local concentration of all the other species). One of the key features of HPC applications is that these same computation(s) get performed for many elements and for many intervals.

#### 1.1.1 Comparisons to Big Data

Another commonly used but poorly defined class of applications of great interest today is *big data*. Big data applications are similar to HPC applications in that they operate on large data sets and demand "high performance", but the performance metrics of interest differ greatly. As a result, the needs of the programmer differ in important ways.

A typical HPC application will run for hours on the same data set, and the most common metric used to compare implementations is the sustained rate at which the computation is being performed, either measured in *FLOPS (floating-point operations per second)* or as a fraction of the theoretical throughput of a given computer system. With the knowledge that the same computations are going to be performed on the same data set many times, an HPC application writer is willing to spend some effort up front to determine the best way to structure the computation and to distribute the data for the particular system on which the application will be run. The cost of this effort is more than paid back over the thousands or millions of iterations performed in the run, but anything the programming model or runtime can do to reduce either the programming time required or the necessary analysis time at application startup is greatly appreciated. Further, it is important that the model give the programmer as much control as possible over how the computation is performed. The optimal approach is likely to be different for every application, and a more generic algorithm that gets 90% of the optimal for a given workload is viewed as "wasting" that last 10%.

In contrast, the target runtime of a common big data application is minutes or seconds (or less!), and it is the response time that is of greatest concern (e.g. for a data analyst getting a response to an interactive query or for a web server to decide what to include in a requested web page). Efficient use of computing hardware resources is still important for big data applications, but the optimization opportunities are greatly reduced compared to the HPC case. The same big data application may be run many times, but the data sets and/or the precise analysis being performed are constantly changing. The return on investment for determining an optimal implementation for a given data set and query is often minimal. As a result, the programmer of a big data application will generally prefer a programming model that allows for rapid iteration and will happily yield control over how the computation is performed to those generic algorithms that provide "good enough" performance on whatever system is available to run the computation.

While Realm is primarily focused on the needs of HPC applications, efforts have been made to

(a) Cray-1 (Deutsches Museum)<sup>1</sup>

(b) Cray Y/MP (CSIRO)<sup>2</sup>

Figure 1.1: Early Cray Supercomputers

anticipate some of the needs of the big data space as well. Virtually everyone agrees that the line between HPC and big data has already started to blur. HPC applications are beginning to include more dynamic behavior and incorporate in-situ analysis capabilities. Big data applications are becoming more computationally intensive as well, and the ability to get the most out of a computer system is becoming more important to keep costs down.

#### **1.2** Supercomputers

In aggregate, a single run of an contemporary HPC application can require the execution of  $10^{10} - 10^{21}$  instructions on a working set that ranges from gigabytes in size up to petabytes. Even if you could somehow fit enough memory into a personal computer to run the application, the larger runs would take days or years to complete. Instead, computer systems are specifically designed for these workloads and are called *supercomputers* (completing our earlier circular definition).

Early supercomputers were custom-designed for the purpose, and looked nothing like a system you might have at your desk. Figure 1.1 shows the distinctive look of some of the more famous Cray systems of the 1970's and '80's. For a number of reasons (cost is perhaps the largest), today's supercomputers are constructed very differently. Instead of being a single monolithic system, a supercomputer today is a *cluster* of hundreds or thousands of smaller computers (often called *nodes*), each of which is similar to what you might find in a high-end personal computer. These individual systems are bolted into racks and the racks are lined up next to each other, generally filling a large room in a building specifically built for these systems. The Titan system takes up 4,352 square feet

<sup>&</sup>lt;sup>1</sup>https://en.wikipedia.org/wiki/Cray-1#/media/File:Cray-1-deutsches-museum.jpg

$<sup>^{2} \</sup>tt http://www.csiro.au/news/newsletters/SIROscope/2010/March10/\tt htm/supercomputing.\tt htm$

of floor space, not counting the space on the floor below for delivering the 9 MW of electricity and on the roof above for dissipating the 9 MW of waste heat.

With the move from custom to commodity computer architecture, the "secret sauce" in a modern supercomputer is now in the interconnection network that allows the individual computers to communicate much more efficiently than the commodity networking (i.e. Ethernet) used in personal computers or data centers. A supercomputer's interconnect makes use of custom hardware (e.g. Infiniband) with much higher peak bandwidth as well as custom software interfaces that allow applications to get data in and out of the network with much less overhead. The programmer of an HPC application must be very careful about when and how much data is moved from one node to another within the cluster if the application is to run well on one of today's supercomputers.

#### 1.3 Bulk-Synchronous Computing

The predominant programming model in use for high performance computing applications today is the *bulk-synchronous* style of computation. In bulk-synchronous computation, a program is conceptually split into a repeating cycle of three phases. (In many implementations, two of the phases may be entangled, but never all three.) Computation phases consist of a hopefully-large number of operations that can be performed without needing the result of any other operations being performed in the same phase. They are followed by communication phases, in which the results of these computations are made available for computations that occur in later phases. Each communication phase is then followed by a synchronization phase, which ensures that all the communication has completed before the next computation phase actually begins. The bulk-synchronous style is a good fit for most HPC applications, as an operation being performed on a large number of elements results in very "wide" computation phases. This ability to place a lot of work within a single computation phase is known as *data-parallelism*.

Some people dislike the use of the term *bulk-synchronous* to describe this approach, as the actual execution is rarely completely synchronous. In nearly all bulk-synchronous implementations, a node is allowed to advance to the next computation phase as soon as it has synchronized with at least the peers with which it interacted in the previous communication phase, allowing minor variations in execution speed to be absorbed. However, assuming the communication graph is connected, the progress of all nodes is ultimately still limited by the slowest node. Our focus in this discussion is on the programming model, and these optimizations do not change the programmer's view, which remains one of alternating phases of computation, communication, and synchronization.

There are two major ways in which bulk-synchronous programming is done. We will start with the more intuitive one which is based on the idea of a *global view of control*. However, we will quickly shift to the *single-program multiple-data* (SPMD) approach, for two reasons. In addition to being (by far) the more common of the two in practice, virtually all compilers for languages with a global

```

#include <upc.h>

1

2

#define GRID_POINTS ...

3

#define TIME_STEPS ...

4

5

shared float [*] T[GRID_POINTS], d2Tdx2[GRID_POINTS];

6

float alpha = ...; /* diffusion coefficient */

7

float dx = ...; /* size of steps between grid points */

8

float dt = ...; /* size of timesteps */

9

10

/* set initial conditions for T[] */

11

12

for(int t = 0; t < TIME_STEPS; t++) {

13

upc_forall(int i = 1; i < GRID_POINTS-1; i++; &T[i]) {

14

float left = T[i - 1];

15

float right = T[i + 1];

16

d2Tdx2[i] = (left + right - 2*T[i]) / (dx * dx);

17

}

18

19

upc_forall(int i = 1; i < GRID_POINTS-1; i++; &T[i])

20

T[i] += alpha * dt * d2Tdx2[i];

21

}

22

```

Figure 1.2: Simulation of heat diffusion in UPC

view of control choose to generate SPMD style code for actual execution.

#### 1.3.1 Global View of Control

Languages that provide a global view of control allow the programmer to write a bulk-synchronous program as if it were executing sequentially, but provide language constructs and/or compiler analysis that is able to mark the boundaries of computation phases, determine what communication must occur and in which phases, and insert the necessary synchronization. Examples of these languages include X10[23], UPC[19], and Chapel[22], and while they differ significantly in their syntax and what other features they provide, they are very similar with respect to the bulk-synchronous programming style.

Figure 1.2 shows a small bulk-synchronous program written in UPC. This is one of the canonical examples of an HPC application, and simulates the diffusion of heat over time along a onedimensional metal bar. Simple UPC programs look nearly the same as C, so we will describe the overall application structure before returning to the specific features of UPC that allow it to parallelize the program across a large supercomputer.

Using the terminology above, the elements in this application are equally spaced grid points along the bar, and there are two properties for each element: the current temperature (T) and an

estimate of the second derivative of the temperature along the length of the bar (d2Tdx2). In UPC, an array is used to store the value of a property for each element, so two arrays are declared on line 6. As is common for HPC applications, the outer loop on line 12 steps through discrete intervals of time. In each interval, both properties are updated for each element. First, the spatial derivative at each location along the bar is estimated based on finite differences (line 16) between the temperature at that location and the temperature at the grid locations to the left and right of the location (lines 14 and 15). This pattern in which is property is updated by accessing properties relative to a given element is often called a *stencil* operation. The spatial derivative is related to the temporal derivative in the heat equation by the diffusion coefficient **alpha**, and line 20 performs explicit integration to update the temperature property based on one timestep's worth of diffusion.

Returning to line 6, there are two pieces of syntax in the array declarations that are part of UPC's extensions to the underlying C language. The **shared** keyword at the beginning declares that these arrays will potentially be shared between different processors in the system (i.e. these are the values that may move during a communication phase). In UPC, each element of a shared array is assigned a "home" location, and the [\*] syntax requests that the arrays be distributed coarsely. The array is divided into chunks of roughly even size, with one chunk being assigned to each processor.

The second UPC language feature used in this program is the upc\_forall loop. It operates like a normal for loop, but is also used to mark the bounds of a computation phase. The optional fourth parameter in the loop header is used to determine which iterations of the loop should be performed by which processor. The expression should evaluate to the address of a shared variable or array element, and the computation is performed by the home processor. The UPC compiler automatically inserts synchronization phases between the computation phases, and uses compiler analysis to determine which subsets of the shared data need to be sent as part of the communication phase.

#### 1.3.2 Single Program Multiple Data

With knowledge of which computations are to be performed on each processor, and what must be communicated, the UPC compiler (along with most other compilers for these languages) effectively generates a new program that will be executed by each processor, in which only its own computation, communication, and synchronization appears. This model in which each process has only a local view and performs explicit communication with other processes is exactly the SPMD approach. Luckily, we don't have to decipher the output of the UPC compiler to get an example — we can instead look a version of the same program written in MPI[58], the most common way that HPC applications are written today.

MPI is a runtime rather than a language, and provides bindings for that allow its use from a host language, such as C or Fortran. There are, however, languages that incorporate SPMD constructs

```

#include <mpi.h>

1

2

#define POINTS_PER_RANK ...

3

#define TIME_STEPS ....

4

5

float T[POINTS_PER_RANK + 2]; /* explicit space for copies of neighbor data */

6

float d2Tdx2[POINTS_PER_RANK];

\overline{7}

float alpha = ...; /* diffusion coefficient */

8

float dx = ...; /* size of steps between grid points */

9

float dt = ...; /* size of timesteps */

10

11

int myrank, nranks;

12

MPI_Comm_rank(MPI_COMM_WORLD, & myrank);

13

MPI_Comm_size(MPI_COMM_WORLD, &nranks);

14

15

/* set initial conditions for T[] */

16

17

for(int t = 0; t < TIME\_STEPS; t++) {

18

if(myrank > 0)

19

MPI_Sendrecv(&T[1], 1, MPI_FLOAT, myrank-1, MPI_ANY_TAG,

20

&T[0], 1, MPI_FLOAT, myrank-1, MPI_ANY_TAG, MPI_COMM_WORLD);

21

if(myrank < (nranks - 1))

22

MPI_Sendrecv(&T[POINTS_PER_RANK], 1, MPI_FLOAT, myrank+1, MPI_ANY_TAG,

23

&T[POINTS_PER_RANK + 1], 1, MPI_FLOAT, myrank+1, MPI_ANY_TAG,

24

MPI_COMM_WORLD);

25

26

for(int i = 1; i \le POINTS_PER_RANK; i++) {

27

28

float left = T[i - 1];

float right = T[i + 1];

29

d2Tdx2[i-1] = (left + right - 2*T[i]) / (dx * dx);

30

}

31

32

for(int i = 1; i \le POINTS_PER_RANK; i++) {

33

34

T[i] += alpha * dt * d2Tdx2[i-1];

}

35

```

Figure 1.3: Simulation of heat diffusion in MPI

directly, such as Coarray Fortran[49]. Figure 1.3 shows the same heat diffusion application written in C with MPI. The bodies of the inner loops remain the same, but virtually everything else is different. The first indication is on line 3, which now defines the number of points per *rank*, the MPI name for one process within the collective performing the overall computation. In fact, the number of grid points in the whole computation does not appear anywhere in the code. Lines 6 and 7 declare the arrays for the properties, but only enough for the data that will be local or, in the case of the T array, with explicit locations for the *ghost copies* of other ranks' data that will be made during the communication stage.

Lines 13 and 14 make calls into the MPI runtime to determine the rank index of the current process and the total number of ranks. Line 18 defines the same top-level loop over time intervals, with the first operation in the MPI version of the loop being an explicit communication phase. The code implicitly assumes that ranks indices are assigned from left to right, and lines 19-21 request a data exchange (both a send and a receive) with the rank to the left, while lines 22-24 do the same with the rank to the right (if it exists). In both cases, the value sent is the one in the edge-most local element, while the value received is stored in the array location created for ghost data.

By default, MPI combines the synchronization phase with the communication phase. Each call to MPI\_Sendrecv suspends execution of a process until the requested data exchange is complete. MPI veterans will note that the code in this example has a major performance bug that results from this automatic synchronization, with the communication phase being split by multiple synchronization phases. It is possible to separate synchronization and communication in many cases in MPI — these will be discussed more in the next chapter.

Computation phases within MPI need no decoration. They are simply code in the host language that operates only on data within the local address space. The **for** loops on lines 26 and 32 therefore only range over the grid points assigned to the current rank. In this case, no communication is necessary between the two loops, and although a synchronization phase could be forced by an explicit call to MPI\_Barrier, it is better to omit it, effectively merging the two computation phases into one. (The UPC compiler can also perform this optimization on the code from Figure 1.2.)

As demonstrated by this code, the SPMD approach involves writing a program that does not describe the entire computation, but only captures a slice of it. The slices executed in each rank must fit together exactly to form the desired overall result. Thus even though the code is written with only a local view, the programmer must clearly still have a global view of the computation in mind. If the global view is required in both cases and compilers exist that can translate from a global view to scalable SPMD code, one might be tempted to ask why programmers would want to perform the translation themselves. One would quickly become involved in a religious debate because there are good arguments on both sides (e.g. reduced programmer effort vs. the ability to interoperate with other code written in the host language) and no objective way to rank them. A more pragmatic answer is to allow both by providing a runtime interface that is reasonably easy for humans to use but also a good target for a source-to-source compiler. A human programmer benefits from an API that limits verbosity and automatically handles obvious cases. In contrast (but critically, not in conflict), a target for compiler output should allow the compiler to express the exact behavior it intends and should present a performance model that the compiler can reason about. MPI does a good job of this, and many source-to-source compilers have chosen to target it. The design of Realm attempts to strike the same balance.

#### 1.4 Programming Challenges

For applications with sufficient data-parallelism, the bulk-synchronous model has been incredibly successful for writing applications that make efficient use of hardware resources and scale well. However, two challenges are threatening to make matters much more complicated. Neither is new, but the severity of both has increased dramatically in recent years and is likely to increase further in the future. We will examine the effect of communication latency in Chapter 2 and of heterogeneity in Chapter 3, and the discussion will include ways in which the bulk-synchronous model has or could adapt to these challenges. With sufficient effort, any given application can likely be tuned for any current or proposed future supercomputer within the bulk-synchronous model. However, what is lost is performance portability. Each combination of application and target machine will need its own version of source code, dramatically increasing software development and maintenance costs, creating a bottleneck on the one resource that is not growing exponentially — human programmers.

No programming system can eliminate programmer effort entirely, but Realm's composable asynchrony and abstractions for functional portability directly address these two challenges, restoring performance portability and allowing a single collection of source code to run well on current as well as future supercomputers.

### Chapter 2

## The Latency Gap

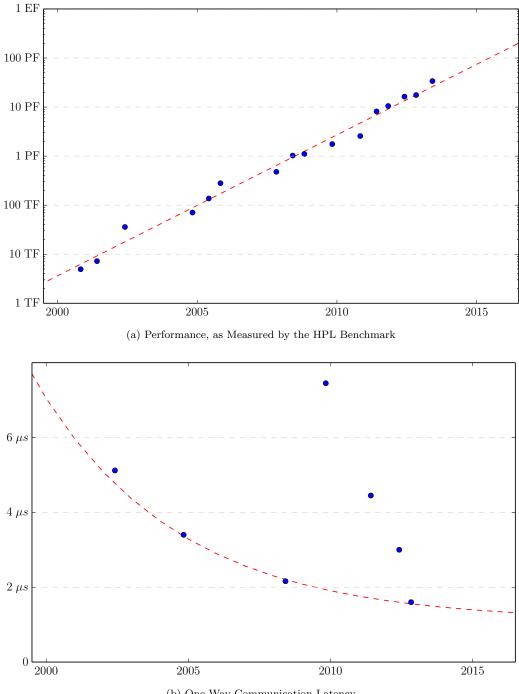

When it comes to high performance computing, the laws of physics are both friend and foe. On the one hand, they tell us that if you can make transistors smaller, they will switch faster and use less power. This has spurred ongoing investment in silicon process technology, and a steady exponential growth in transistor performance famously described by Intel's Gordon Moore in 1965. Although initially just an observation, this expectation of exponential growth has become ingrained for both computer architects and computer users. As silicon process improvements have slowed down in the past few years, researchers have looked for (and found) other ways to "preserve Moore's Law". Indeed, much of the heterogeneity challenge discussed in the next chapter is the direct result of attempts to get "moore" out of each transistor. The end result can be seen in Figure 2.1a, which shows a continued exponential trend in the performance of the world's top supercomputer, as tracked in the twice-annual Top500 list[63].

Unfortunately, transistors are not the only component of a supercomputer. To be useful, these transistors must communicate with each other. The same physics that gives us (indirectly) Moore's Law also gives us the laws of thermodynamics and electromagnetics. Transistors generate heat but also have to be kept reasonably cool (ideally around room temperature) to guarantee proper functionality. Thermodynamics places a limit on how many transistors can be placed within a given volume, and if you want more transistors than that, you must spread them apart to keep them cool. This isn't a problem on its own — Moore's Law applies to a server room just as well as to a single chip — but electromagnetics places a hard lower bound on the time it takes for transistors on opposite sides of the room to communicate. Communication also requires time spent in software and hardware, and that portion of the communication latency has significantly improved over time, as shown in Figure 2.1b. However, no improvements to either software or hardware will ever reduce the communication latency below the 500 nanoseconds it takes a photon to travel the 60 meters from one end of a supercomputer cluster to the other.

(b) One-Way Communication Latency

Figure 2.1: Performance and Latency of World's Fastest Supercomputers

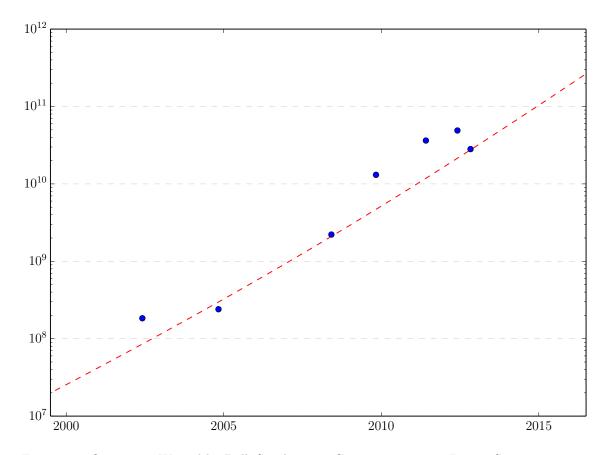

Figure 2.2: Operations Wasted by Bulk-Synchronous Communication on Fastest Supercomputers

The combination of exponential transistor performance and only asymptotically decreasing communication latency has created a *latency gap* that is fatal to the bulk-synchronous style of programming at supercomputing scales. Computation and communication are separated into distinct phases, and those transistors that are so good at computing sit mostly idle during a communication phase. By taking the product of the performance and communication latency for top supercomputers in Figures 2.1a and 2.1b, we obtain the number of potential computation operations wasted by *each* communication phase of a bulk-synchronous program (Figure 2.2). These numbers are huge and perhaps hard to put in context. One way to interpret these numbers is as the average number of instructions that must be executed in the computation phase if a program is to achieve 50% utilization of the system. If the goal is to achieve 90% (a target still considered low by many HPC users), the number is 10 times larger than that, passing through one trillion a few years ago and likely to exceed one quadrillion on the next set of supercomputers. Only the most contrived applications have sufficient data-parallelism to manage that.

```

/* initialization is the same as before */

1

2

for(int t = 0; t < TIME_STEPS; t++) {

3

int nreqs = 0;

4

MPI_Request mpi_reqs[4];

5

/* initiate MPI sends and receives */

6

if(myrank > 0) {

7

MPI_Isend(&T[1], 1, MPI_FLOAT, myrank-1, ..., &mpi_reqs[nreqs++]);

8

MPI_Irecv(&T[0], 1, MPI_FLOAT, myrank-1, ..., &mpi_reqs[nreqs++]);

9

10

ł

if (myrank < (nranks - 1)) {

11

MPI_lsend(&T[POINTS_PER_RANK], 1, MPI_FLOAT, myrank+1, ..., &mpi_reqs[nreqs++]);

12

MPI_Irecv(&T[POINTS_PER_RANK + 1], 1, MPI_FLOAT, myrank+1, ..., &mpi_reqs[nreqs++]);

13

14

}

15

/* overlap portion of computation phase that does not need ghost data */

16

for(int i = 2; i \le POINTS_PER_RANK - 1; i++) {

17

float left = T[i - 1];

18

float right = T[i + 1];

19

d2Tdx2[i-1] = (left + right - 2*T[i]) / (dx * dx);

20

}

21

22

/* now perform synchronization phase */

23

MPI_Waitall(nreqs, mpi_reqs, MPI_STATUS_IGNORE);

24

25

/* edges can be performed only after synchronization phase is complete */

26

d2Tdx2[1] = (T[0] + T[2] - 2*T[1]) / (dx * dx);

27

d2Tdx2[POINTS_PER_RANK] = (T[POINTS_PER_RANK - 1] + T[POINTS_PER_RANK + 1] - T[POINTS_PER_RANK] = (T[POINTS_PER_RANK - 1] + T[POINTS_PER_RANK - 1] + T[POINTS_PER_RANK - T[P

28

2 * T[POINTS_PER_RANK]) / (dx * dx);

29

30

for(int i = 1; i \le POINTS_PER_RANK; i++) {

31

T[i] += alpha * dt * d2Tdx2[i-1];

32

33

ł

```

```

Figure 2.3: Simulation of heat diffusion with latency hiding

```

#### 2.1 Hiding Latency

Although the current "hyperinflationary" period is a recent occurrence, the risk that communication latency presents to bulk-synchronous programming has been apparent to programmers and researchers for a long time. Every HPC programmer is taught that they need to *overlap* their communication and computation to hide the latencies in modern systems. Virtually every language or runtime for bulk-synchronous programming has been extended to allow this overlap in some form. We will start with a concrete example of how overlap is achieved, and then generalize to discuss the merits and drawbacks of the approach. Recall from the previous chapter that communication primitives in MPI include synchronization phases by default. MPI allows the synchronization to be separated from the communication through the use of *non-blocking* versions of most primitives<sup>1</sup>. Figure 2.3 shows the timestepping loop of our running heat diffusion example, implemented with these non-blocking primitives. The first indication that non-blocking MPI communication is being performed is the declaration of an array of MPI\_Request objects on line 5. These objects are used to track the state of overlapped communication. Lines 7-14 use MPI\_Isend and MPI\_Irecv to initiate the exact same sends and receives that were performed by the MPI\_Sendrecv calls before. (For some reason, there is no MPI\_Isendrecv in MPI.) Each call fills in its own MPI\_Request object, and the nreqs variable is used to keep track of how many there are. These calls return immediately (i.e. they do not *block* the caller), allowing the data transfers to proceed concurrently with additional application code that appears before the synchronization phase.

Because it is overlapped with the communication, that portion of the application code must not read from the memory locations that are receiving data nor write to the locations from which sends are occurring. As it is only a runtime library, MPI cannot check that these rules are followed. When the rules are not followed, the resulting bugs cause non-deterministic failures that can be very challenging to fix and often remain latent in applications for years, just waiting for a system with the right performance characteristics to appear. In this case, only the first and last iterations of the stencil-calculating loop need the data from the communication phase, and by restricting the loop bounds slightly, the bulk of the loop (lines 17-21) can safely be computed concurrently with the communication phase.

Line 24 performs the synchronization phase, asking the MPI runtime to wait until the nonblocking communication has completed. Once the call to MPI\_Waitall has returned, it is safe for lines 27 and 28 to read from T[O] and T[POINTS\_PER\_RANK + 1] and for line 32 to overwrite the values sent. In a perfect world, enough time was spent doing useful work in lines 17-21 that the call to MPI\_Waitall can return immediately, keeping the processors fully utilized.

The key observation that makes latency hiding work is that data-parallelism is not the only kind of parallelism available in most applications. Different operations performed by the application may be performed concurrently if they do not *depend* on each other. The most obvious form of dependency is a data dependency (e.g. reading the value written by the other operation), but many other forms of dependencies can exist, such as a conflict on a common software or hardware resource. Using the generic term *task* to describe some collection of operations, the availability of independent tasks in an application is called *task-parallelism*.

Our initial implementation of the heat diffusion simulation could be considered to have two tasks (stencil computation and temperature update), but lacked any task-parallelism. However,

<sup>&</sup>lt;sup>1</sup>These primitives are sometimes described as being "asynchronous". We follow MPI's lead here and stick with "non-blocking", in part because we argue these operations are still carefully synchronized with the calling code, and in part because we wish to reserve the "asynchronous" term for a qualitatively different approach to come.

by splitting the single stencil computation into two tasks, one operating on the interior and one on the boundary, we were able to expose the independence between the interior stencil and the preceding temperature update tasks on other ranks. The boundary stencil still depends on the remote temperature updates, but the interior computation can proceed while the boundary one waits for communication and synchronization with the other ranks. This pattern of exposing taskparallelism through an interior/boundary split is a favorite in HPC applications, in part because it is easy for compilers and/or libraries to assist with the transformation.

While data-parallelism in an HPC application tends to scale with the number of elements, taskparallelism tends to scale with the number of properties that exist per element. For today's and future supercomputers, neither task-parallelism nor data-parallelism is sufficient. A programming model must take full advantage of both to bridge the latency gap.

Automatic identification of dependencies between tasks is intractable in general languages such as C, C++, and contemporary Fortran<sup>2</sup>, and assistance from the programmer is needed. There are many different ways in which models ask the programmer to describe the dependencies that exist between operations within the application. The property we focus on here is whether the dependencies themselves are *implicit* or *explicit*. As the name suggests, a model using *explicit dependencies* provides language and/or runtime constructs to explicitly name pairs of dependencies are not spelled out, but are instead implied by other language or runtime constructs, often related to scheduling. We discuss both in more detail below, as the choice between implicit and explicit dependencies is not just a matter of aesthetics for the programming model — it impacts the performance portability of applications written in that model.

#### 2.2 Implicit Dependencies

Models based on implicit dependencies are easily identified through their use of non-blocking operations. Constructs are provided that allow the caller to initiate work and then to wait on the completion, ideally after performing enough other work to hide the latency of the non-blocking operation. This approach has two major benefits. First, it is a relatively simple model for programmers to understand. Delegating work to another (and often needing to wait for the work's completion) is something humans do on a daily basis. Second, the introduction of non-blocking operations is an evolutionary path that allows a language or runtime that lacked latency hiding capabilities to add it in a minimally disruptive way.

Unfortunately, having an application wait on the completion of one operation so that it can safely execute another is a fundamental flaw that prevents code written in these languages or runtimes from being performance portable. To understand why, it helps to look at how the dependencies between

$<sup>^{2}</sup>$ Earlier versions of Fortran were much more amenable to compiler analysis, and there are some that advocate for a return to such simpler days.

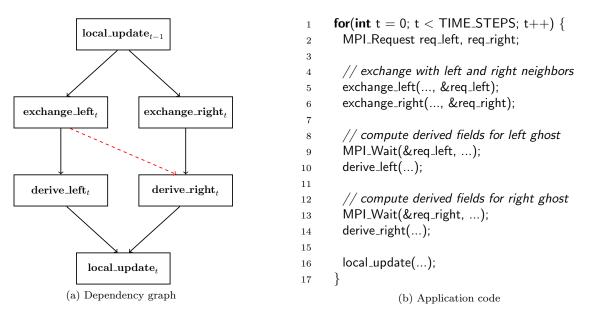

Figure 2.4: Undesired scheduling constraints resulting from implicit dependencies

tasks are described in these systems. As we saw in the MPI example above, if a dependency exists between two tasks, a correct application must wait on the completion of the first task sometime before executing the second. However, the converse is not universally true. The fact that a task is executed after the application has waited on an earlier task does not guarantee a dependence exists. As an example, consider a minor variation of our MPI example in which the local computation uses fields derived from the ghost values rather than the ghost values themselves. The derivations for different ghost cells are independent, but there is no way to precisely express that independence with application waits. Figure 2.4a shows the desired dependency graph with solid black arrows, but the ordering of the code (Figure 2.4b) implies the undesired red arrow as well, as the call to derive\_right on line 14 follows the wait on req\_left on line 9. If the exchange of the right ghost cells is likely to complete before the exchange of the left, the red arrow can be switched by moving lines 13-14 above lines 9-10, but no ordering of the code will be free of undesired dependencies.

As a result, a system in which application waits are used to implicitly encode dependencies between tasks has very little freedom to make scheduling decisions, because the system has no way of knowing which tasks before and after a wait are dependent. Virtually all decisions must be made by the programmer. Worse, the decisions are implemented by a manual reordering of the application code and wait operations. For applications that were ported to Titan as part of the acceptance testing, this manual code restructuring was estimated to account for 70-80% of the person-years of developer time per application[18]. Quite often, the pieces of code being reordered come from different parts of the source code, requiring a large amount of effort and destroying the modularity of the code. Finally, if a different scheduling of tasks is needed for two different systems (one might have faster processors, while the other has a faster interconnect), two different versions of the source code are needed to capture those two schedulings.

#### 2.3 Explicit Dependencies

If one is willing to step outside of the standard bulk-synchronous paradigm, a significant portion of the problem of scheduling tasks to hide latency can be moved to the compile and/or runtime in a system that uses *explicit dependencies*. When every task is explicitly annotated with the set of tasks on which it depends, the order in which tasks are launched by the application does not limit the possible schedules. A single version of the source code describes all valid schedules, and the compiler or runtime has the maximum possible freedom in selecting a schedule that will run most efficiently on a given system.

A natural way to consider an application's collection of tasks and their dependencies is as a graph, with nodes in the graph representing tasks and edges between nodes representing explicit dependencies between two tasks. When designing a model based on explicit dependencies, the first decision that must be made is whether than graph is constructed and analyzed at compile time, at runtime, or some combination of the two. Most systems that use explicit dependencies fall at the more static (i.e. compile-time) end of the spectrum. Fully static approaches use the operation graph within the compiler, generating code for machine (or sometimes lower-level runtimes) that are unaware of the boundaries between tasks and their dependencies. By doing all the analysis and optimization at compilation time, any runtime overhead due to the use of explicit dependencies can be minimized. However, that analysis (and the optimizations that result from it) suffers from the standard limits of static analysis: the behavior of application code is often impossible to capture precisely, especially when it might depend on the exact inputs to a given run.

Some of those limitations can be addressed by augmenting the compile-time static analysis with some dynamic analysis at runtime. For example, the compiler's analysis might be limited to smaller subgraphs which may be instantiated at runtime based on the data set being operated on.

The dynamic end of the spectrum, in which task graphs are constructed and analyzed entirely at runtime, is much more sparsely populated. A heavy bias towards compile-time analysis is natural in the high performance computing space, where applications tend to be regular and run for a long time. Compile-time overhead that can be amortized over thousands or millions of iterations is strongly preferred over run-time overhead that is incurred on every iteration. However, as applications and machines both become larger and more dynamic, the limits of static analysis create a gap between theoretical and achieved performance. As that gap grows, so does the willingness of an HPC user to accept some run-time overhead in exchange for improvements in scheduling efficiency, programmer productivity, and of course portability. A fully dynamic approach based on explicit dependencies must deal with several challenges. First, and most obviously, the runtime overhead must be as low as possible. The costs involved in creating, storing, analyzing, and ultimately destroying the operation graph must be small, and must scale well to very wide and/or very deep task graphs. The common strategy used by all of the runtimes discussed in the next section is to execute the task graph as it is being constructed, keeping only a frontier of the graph that ideally includes only the tasks that have not yet been executed. Without the whole graph available, any scheduling (what to run next) or mapping (where to run it) decisions made by the runtime must necessarily be local decisions.

This leads to another major challenge for dynamic approaches. The frontier of the task graph must include enough parallelism that good local scheduling or mapping decisions are even possible. The key to this is to make sure the application is able to "run ahead" of the actual execution, enumerating tasks in a programmer-friendly way (e.g. depth-first traversal of one components tasks before moving on to the next component). Explicit dependencies allow the enumeration and execution of tasks to be asynchronous, but the maximal benefit is obtained when all dependencies are explicit. Any application dependency that cannot be expressed explicitly requires some other task to wait before launching it, and this wait brings back all the drawbacks of the implicit dependency model. The programmer must again reason about what parts of the task graph might be hidden behind the wait and whether they need to be manually reordered to expose independent work in the task graph's frontier to fully utilize the system.

#### 2.4 Microprocessor Design Analogy

The concepts of implicit and explicit dependencies can be seen in many other fields. For those who study microprocessor design, they are familiar in the difference between *in-order* and *out-of-order* architectures. In nearly all microprocessor designs, a pipelined architecture is used to improve the processor's clock speed while maintaining high instruction throughput. As a result, multiple instructions will be in different stages of execution at the same time. A later instruction may depend on the result of a previous instruction that is still in the pipeline, and must *stall* until the data is ready.

Designs that use in-order execution suspended the entire instruction stream in such a case, stalling all following instructions as well. Based on knowledge of the pipeline depth, a compiler that generates code for an in-order architecture can usually select an order of instructions that minimizes the stalls for results of arithmetic instructions, but inputs that come from memory loads depend on cache behavior and are hard to predict at compile time.

As the cost of a cache miss grew (another latency gap!), microprocessor design moved to outof-order execution. In these designs, an instruction whose input data was not ready could be set aside, allowing instructions later in the instruction stream to be decoded and hopefully executed. An instruction that is set aside is annotated (a variety of techniques exist, including many based on Tomasulo's algorithm[62]) with the exact list of earlier instructions that must complete before the later instruction can be dispatched. This choice between an in-order and out-of-order design requires making the same sorts of trade-offs between performance, cost, and portability that we have discussed here.

#### 2.5 Related Work

Virtually every language or runtime system used for high-performance computing includes mechanisms that attempt to address the problems caused by the latency gap. Most are based on implicit dependencies. Our examples of non-blocking communication in this chapter used the MPI[58] runtime, but other communication libraries such as GASNet[66] handle it similarly.<sup>3</sup> Languages that use implicit dependencies include the previously-discussed UPC[19], Chapel[22], and X10[23] as well as others such as Cilk[11], Titanium[67], and the Habanero family of languages[21]. Runtimes that make use of GPUs as accelerators, either for graphics (e.g. OpenGL[37] or Direct3D[47]) or for general-purpose computation (e.g. CUDA[50] or OpenCL[38]), all use implicit dependencies to hide the latencies associated with initiation work on and communicating with the GPU. Syntax and, more importantly, the choice of which operations are available in non-blocking form, can vary quite a bit between these languages and runtimes, but the basic approach of initiating a non-blocking operation and then some time later waiting on its completion is common to all.

For explicit dependencies, the spectrum between static and dynamic handling of the dependency graph allow for much more diversity. The static end of the spectrum includes Sequoia[33] and Deterministic Parallel Java (DPJ)[12]. DPJ uses the graph to identify sections that can be run on separate threads managed by the operating system. In contrast, Sequoia uses a performance model of the target machine to compute an exact execution schedule for all tasks and data movement during compilation.

Many systems perform dataflow analysis (generally coarse-grained) to extract what amount to templates for subgraphs of the task graph, allowing efficient instantiations of those templates at runtime to construct the overall graph[36, 59, 2, 26]. Concurrent Collections[15] makes these dataflow templates an explicit part of the language. Most of these systems do include some runtime component, but that component is not directly aware of the task graph.

At the fully dynamic end of the spectrum, there are three major research efforts in addition to Realm. OmpSs[31] uses a custom compilation flow that adds directives to existing host languages (C, C++, Fortran) that allow pieces of code in a function to be *outlined* into separate tasks, which may execute concurrently with the caller or with each other. Tasks are annotated with their inputs and outputs. Based on the directives, the compiler generates code that performs calls into the OmpSs

<sup>&</sup>lt;sup>3</sup>Realm uses only a subset of the GASNet API calls to avoid the pitfalls associated with implicit dependencies.

runtime to launch tasks and provide the locations of the task's inputs and outputs. The runtime can then compare the locations with that of other tasks to determine the inter-task dependencies.<sup>4</sup> The OmpSs runtime includes a scheduler that tracks which tasks are ready to run and selects from that set when processor(s) become available. OmpSs supports execution on multiple systems in a cluster, but does so using a master/worker model in which all task graph analysis is performed on the master[60].

StarPU[3] is a purely library based runtime. The programmer of a StarPU application writes in C or C++ and manually inserts calls into the StarPU runtime to create tasks, to attach buffers for input and output, and to submit the task for execution. As with OmpSs, the StarPU runtime deduces the explicit dependencies between task based on accesses to common buffers, and then performs both scheduling and mapping of the tasks once those dependencies have been satisfied. Originally designed to address challenges related to heterogeneity (which we will discuss in the next chapter), a StarPU runtime only manages a single node. For an application to run on a cluster, a so-called *hybrid* programming model is used, combining StarPU with MPI. In addition to the other challenges with a hybrid model (discussed in the next chapter), this approach limits the benefits of using explicit dependencies to just tasks that run on the same node.

A recent extension to StarPU, StarPU-MPI[1] encapsulates the hybridization by allowing StarPU tasks to attach input buffers that may reside on other ranks. The application may choose an *owner* for each buffer (this is similar to Chapel's *domain maps* and more expressive than X10 or UPC's distribution mechanisms) and uses the standard *owner-computes* model in which tasks are executed on the rank that owns the output buffer(s). The StarPU-MPI runtime on each rank automatically inserts the necessary MPI communication and synchronization primitives to connect with producer or consumer tasks on other ranks, but to do so, it must know which tasks those are. This forces a deviation from the single-program multiple-data model, as each rank must include those remote producers and consumers as part of its program. (The runtime knows not to execute them due to the owner-computes rule.) The safest thing to do is to give each rank a global view of the program's task graph, but scalability results show that *pruning* of the graph on each rank is absolutely necessary for running on systems larger than 1000 nodes or so. Unfortunately, this pruning must be done by the programmer and is vulnerable to the same sorts of missed synchronization bugs that occur in implicit dependency models.

The third active effort in the space of runtime systems based on dynamic explicit dependencies is the Open Community Runtime (OCR)[52]. OCR is also library based and does not directly include a compiler component. However, it is not designed for direct use by human programmers either. Instead, it is expected that OCR programs are the output of source-to-source compilation

<sup>&</sup>lt;sup>4</sup>One might argue that the task dependencies are only implicitly described through these data interactions. However, the key distinction we are interested in is whether a "producer" and a "consumer" are directly connected through an explicit linkage or if their connection is only implied by connections of both producer and consumer back to their parent task.

from other programming languages. For example, OCR completely prohibits the use of application waits (except for debugging purposes), demanding the use of a *continuation-passing-style* of code that is easy for compilers to mechanically produce but very laborious for humans. In addition to explicit dependencies based on use of common *data blocks*, OCR includes several kinds of explicit event objects that can be used to define other dependencies between tasks. OCR is intended to work for clusters but assumes a homogeneous system architecture. It presents a logically centralized scheduler that has a global view of the system and manages the mapping of tasks and any necessary data movement.

All three of these systems focus on explicit dependencies between tasks, but lack the ability to describe explicit dependencies between tasks and other operations such as memory allocation or explicit data movement. In some cases, this shortcoming can be addressed by encapsulating the other operations inside a task (at some cost). In others, this lack of composability results in application waits to guarantee correctness.

### Chapter 3

## Heterogeneity

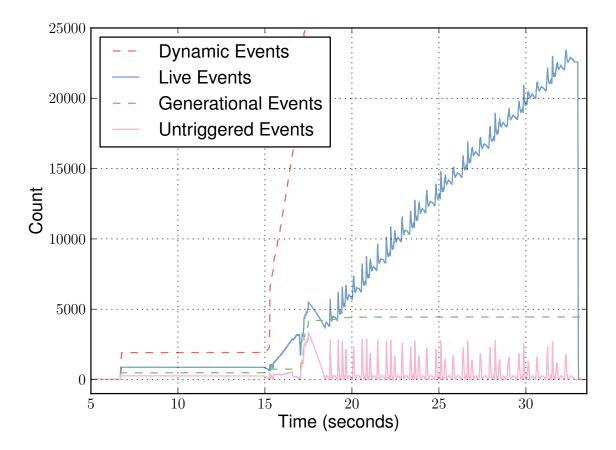

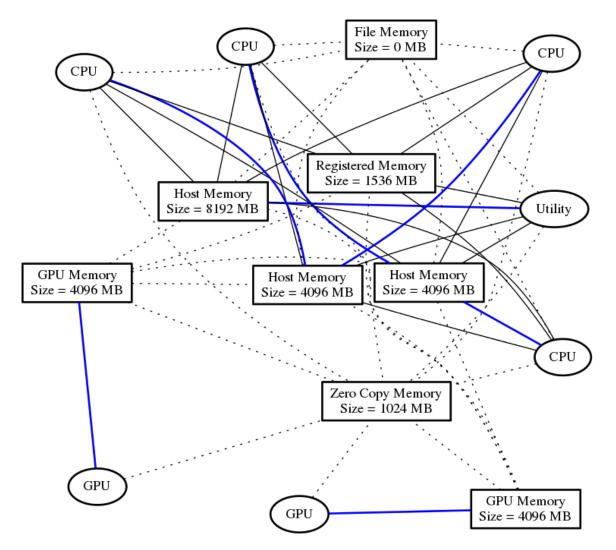

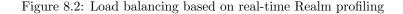

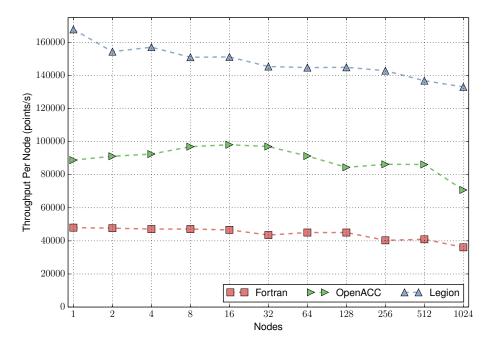

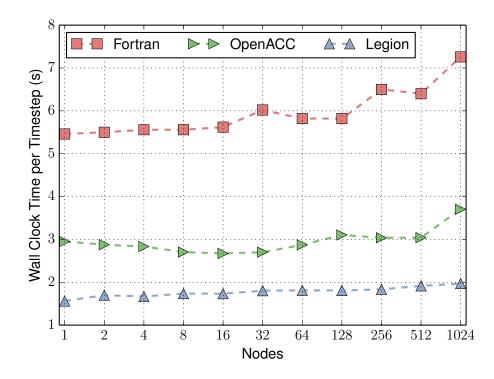

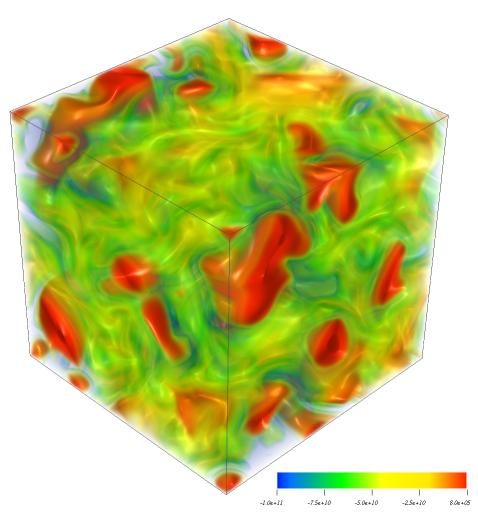

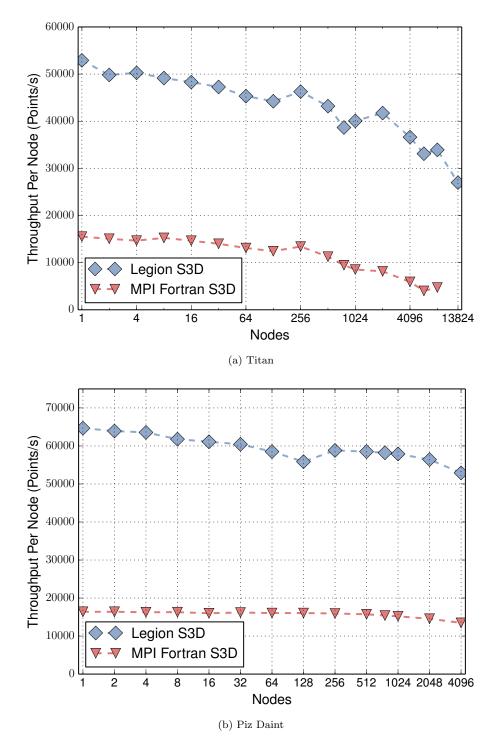

The second major challenge faced by the bulk-synchronous programming paradigm is the dramatic increase in the complexity and critically, heterogeneity, of both supercomputer system architectures and the workloads that are being run on them.